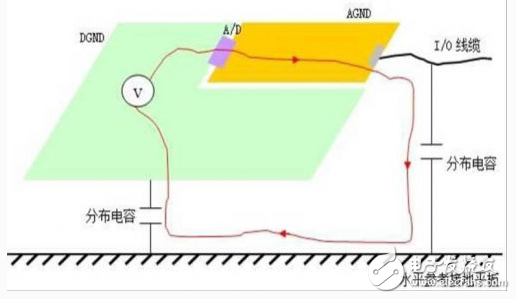

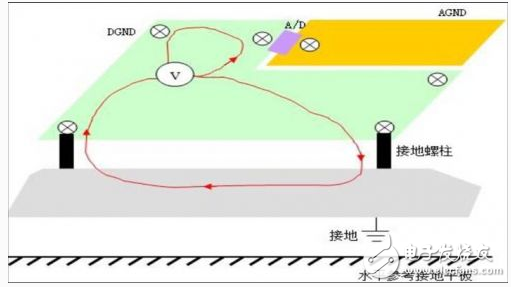

In the process of digital-to-analog design, it is necessary to avoid the experience and rules. However, to thoroughly explain this problem, we must first understand the mechanism of digital-to-analog interference. The effect of digital on simulation can be divided into the following two cases: Crosstalk is generally influenced by the distribution parameters between the digital and analog signal lines, but this problem is at least not very prominent at present. Since the digital signals are to be placed in the digital area, the analog signals are placed in the analog area, and the space has been isolated, so the risk is reduced. Common impedance coupling is caused by the fact that the disturbance source shares a line impedance with the sensitive part. When the digital signal is co-located with the analog signal, since the ground line has a certain impedance at high frequencies, a digital voltage will generate a voltage drop when it flows back. This is the common mode voltage source. At this time, if the common mode current flows through the analog region, a voltage drop is generated on the ground of the analog region. If this voltage is superimposed on the analog signal, it will affect the analog signal, which is the mechanism of digital-to-analog interference. A, reduce the GND impedance, reduce the common mode voltage source; B. Avoid the common mode current generated by the digital GND flowing through the analog area. For reducing the GND impedance, the impedance of the extreme point is zero. Even if the digital signal flows back, the common mode voltage source will not be generated, and therefore, the analog signal will not be affected. However, the actual situation is that the GND zero impedance can not be achieved, the only means is to make it unlimited reduction, such as using the GND plane, the GND plane to reduce the division, the GND plane aspect ratio is less than 3, and so on. For the digitally generated common mode current does not flow through the analog region, the digital-analog segmentation revelation is the original intention. But the reality is that there are many cases where the numbers and simulations are segmented, but the digital interference with the simulation is still not solved. Here, we need to emphasize that if we only want to solve the influence of numbers on simulation through digital-analog division, it is the wrong way of not seeing the trees. Digital-to-analog partitioning requires in-depth analysis from the system architecture, such as plastic or metal chassis, system grounding points, analog area with or without I/O cables, and so on. E.g: For plastic chassis, if the analog area has I/O cables, digital analog segmentation may not solve the problem. Because the common mode noise generated by the digital signal on GND will form a loop due to the distributed parameters of the I/O cable and the reference ground plane, the common mode current will also flow through the analog region, so this segmentation poses a great risk. For metal-clad products, because the boards need to be grounded, it is important to focus on the grounding point, that is, the grounding point is set to avoid the digital area common-mode current flowing through the analog area. For the case of a cable with no I/O in the analog area, after digital and analog division, the grounding point can be set on the digital/analog GND of the A/D chip to prevent the common mode current in the digital area from flowing through the analog area. However, for the case where there is an I/O cable in the analog area, because of the distribution parameters of the cable to the ground, there is a risk that the common mode current flows through the analog area. At this time, the length of the I/O cable needs to be fully considered, such as Because the audio earphone cable is short, it may not be risky after splitting, but if the cable is very long, even the style is very risky. Nothing is absolutely correct, and the same is true for digital-to-analog. If it is not good, it will have negative effects, such as cross-segment wiring. In addition, even if it is divided at a high frequency, there is a distribution parameter between the divisions, and therefore, division in a complete sense cannot be formed. For beginners or engineers who know little about EMC, if the digital model style is not accurate, it is recommended to minimize or simply not split to ensure that the GND plane is complete and reduce the GND plane impedance, which can also reduce the risk of digital interference. Double Burner with Built in Hob Gas Stove 2 Burner,Double Burner Gas Cookers,Brass Burner Stoves,Double Burner Gas Stove xunda science&technology group co.ltd , https://www.gasstove.be